# **Operating Systems**

Memory Management

#### Overview

• Provide Services (done)

- processes (done)

- files (after memory management)

Manage Devices

processor (done)

- memory (next!)

- disk (done after files)

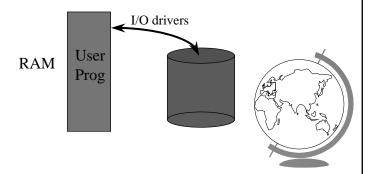

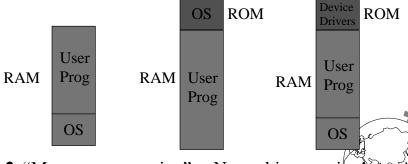

# Simple Memory Management

- One process in memory, using it all

- each program needs I/O drivers

- until 1960

- Small, protected OS, drivers

- DOS

- "Mono-programming" -- No multiprocessing!

- Early efforts used "Swapping", but sloooow

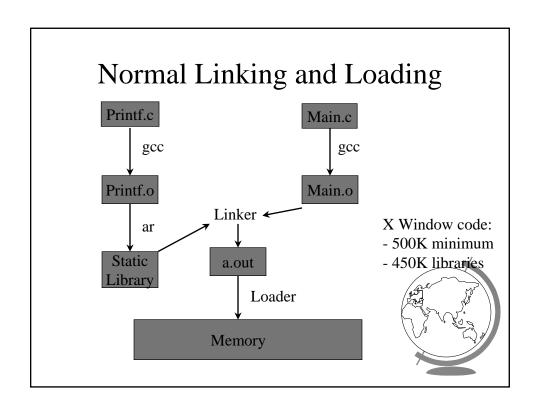

| IVIC              |     | <b>'</b> | mparis                  | Perform<br>ons          | iance             |

|-------------------|-----|----------|-------------------------|-------------------------|-------------------|

| Linking<br>Method |     |          | Run<br>Time<br>(4 used) | Run<br>Time<br>(2 used) | Run Time (0 used) |

| Static            | 3Mb | 3.1s     | i i                     | 0                       | 0                 |

| Load<br>Time      | 1Mb | 3.1s     | 0                       | 0                       | 0                 |

| Run<br>Time       | 1Mb | 1.1s     | 2.4s                    | 1.2s                    | 0                 |

# Design Technique: Static vs. Dynamic

- Static solutions

- compute ahead of time

- for predictable situations

- Dynamic solutions

- compute when needed

- for unpredictable situations

- Some situations use dynamic because static too restrictive (malloc)

- ex: memory allocation, type checking

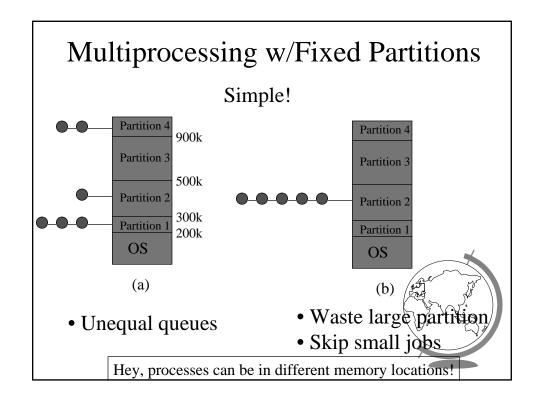

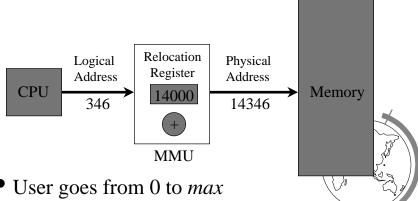

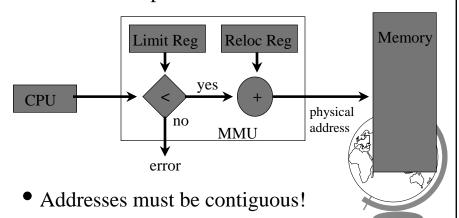

# Logical vs. Physical Addresses

- Compile-Time + Load Time addresses same

- Run time addresses different

- User goes from 0 to *max*

- Physical goes from R+0 to R+*max*

#### Relocatable Code Basics

- Allow *logical* addresses

- Protect other processes

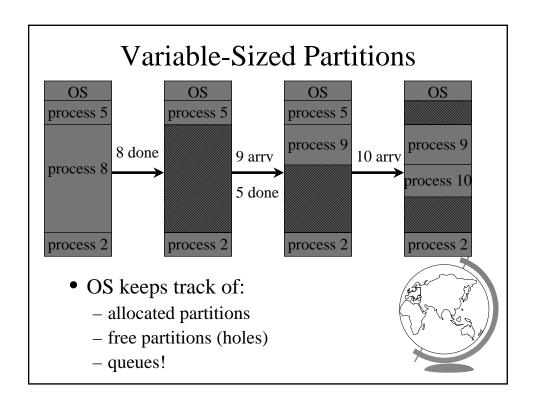

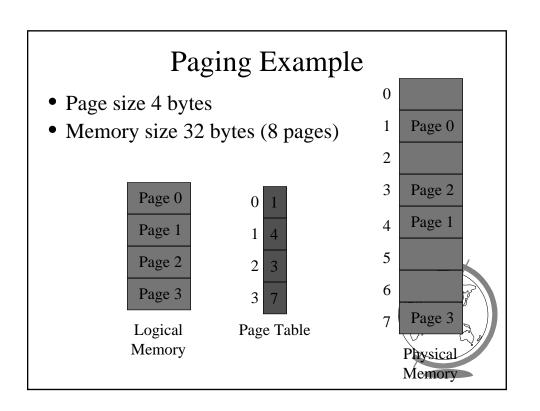

#### Variable-Sized Partitions

- Idea: want to remove "wasted" memory that is not needed in each partition

- Definition:

- Hole a block of available memory

- scattered throughout physical memory

- New process allocated memory from hole large enough to fit it

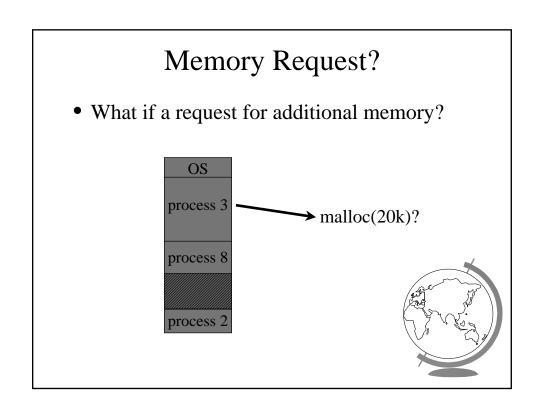

## **Internal Fragmentation**

Have some "empty" space for each processes

Internal Fragmentation - allocated memory may be slightly larger than requested memory and not being used.

## **External Fragmentation**

• External Fragmentation - total memory space exists to satisfy request but it is not

# Analysis of External Fragmentation

- Assume:

- system at equilibrium

- process in middle

- if N processes, 1/2 time process, 1/2 hole

- + ==> 1/2 N holes!

- Fifty-percent rule

- Fundamental:

- + adjacent holes combined

- + adjacent processes not combined

# Compaction

- Shuffle memory contents to place all free memory together in one large block

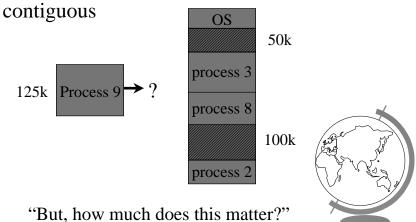

- Only if relocation dynamic! • Same I/O DMA problem (a) (b) OS OS OS 50k process 3 90k process 3 process 8 125k Process 9 60k process 8 process 8 100k process 3 process 2 process 2 process 2

# **Cost of Compaction**

- 128 MB RAM, 100 nsec/access

- → 1.5 seconds to compact!

- Disk much slower!

#### Solution?

- Want to minimize external fragmentation

- Large Blocks

- But internal fragmentation!

- Tradeoff

- Sacrifice some internal fragmentation for reduced external fragmentation

- Paging

#### Where Are We?

• Memory Management

- fixed partitions (done)

linking and loading (done)

variable partitions (done)

• Paging ←

• Misc

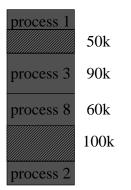

# **Paging**

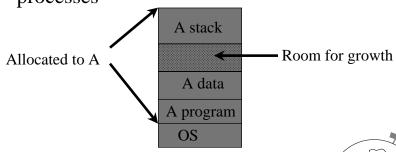

- Logical address space noncontiguous; process gets memory wherever available

- Divide physical memory into fixed-size blocks

- + size is a power of 2, between 512 and 8192 bytes

- + called Frames

- Divide logical memory into bocks of same size

- + called Pages

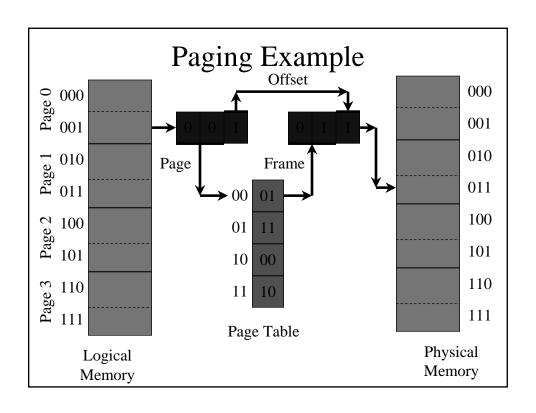

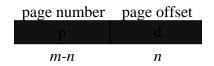

# Paging Hardware

- address space 2<sup>m</sup>

- page offset 2<sup>n</sup>

- page number 2<sup>m-n</sup>

• note: not losing any bytes!

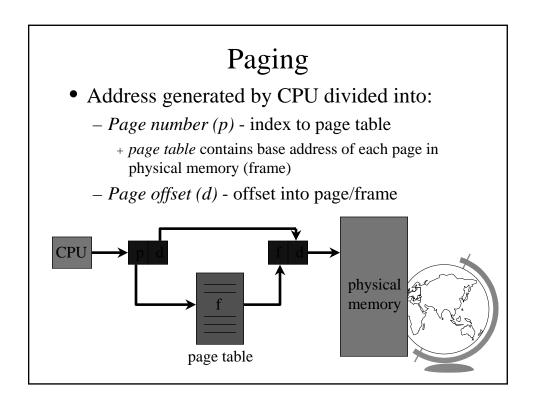

## Paging Example

- Consider:

- Physical memory = 128 bytes

- Physical address space = 8 frames

- How many bits in an address?

- How many bits for page number?

- How many bits for page offset?

- Can a logical address space have only pages? How big would the page table be

#### Another Paging Example

- Consider:

- 8 bits in an address

- 3 bits for the frame/page number

- How many bytes (words) of physical memory?

- How many frames are there?

- How many bytes is a page?

- How many bits for page offset?

- If a process' page table is 12 bits, how many logical pages does it have?

# Paging Tradeoffs

- Advantages

- no external fragmentation (no compaction)

- relocation (now pages, before were processes)

- Disadvantages

- internal fragmentation

- + consider: 2048 byte pages, 72,766 byte proc

- -35 pages + 1086 bytes = 962 bytes

- + avg: 1/2 page per process

- + small pages!

- overhead

- + page table / process (context switch + space)

- + lookup (especially if page to disk)

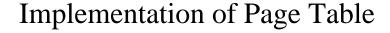

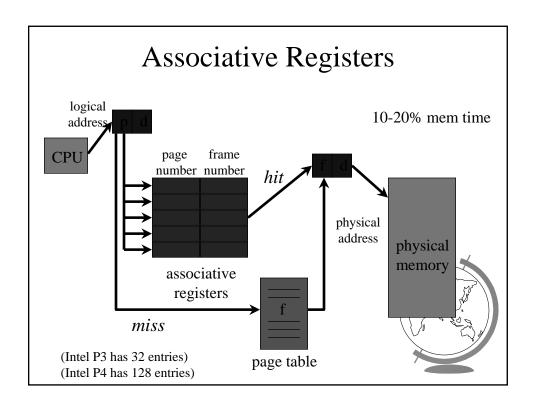

# Implementation of Page Table

- Page table kept in registers

- Fast!

- Only good when number of frames is small

- Expensive!

- Page table kept in main memory

- Page Table Base Register (PTBR)

Logical Memory

Page Table

Physical Memory

- Page Table Length

- Two memory accesses per data/inst access

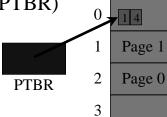

- Solution? Associative Registers

## Associative Register Performance

• *Hit Ratio* - percentage of times that a page number is found in associative registers

#### <u>Effective access time = </u>

#### hit ratio x hit time + miss ratio x miss time

- hit time = reg time + mem time

- miss time = reg time + mem time \* 2

- Example:

- 80% hit ratio, reg time = 20 nanosec, men time = 100 nanosec

- -.80 \* 120 + .20 \* 220 = 140 nanosecond

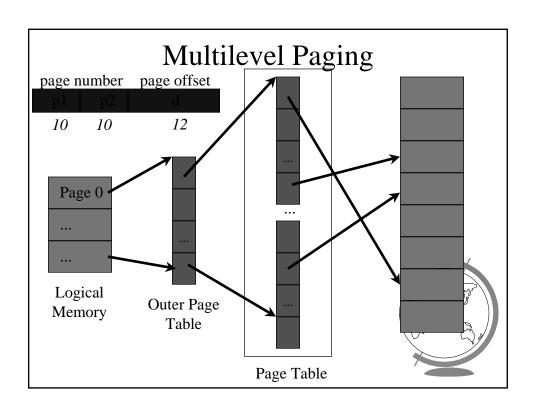

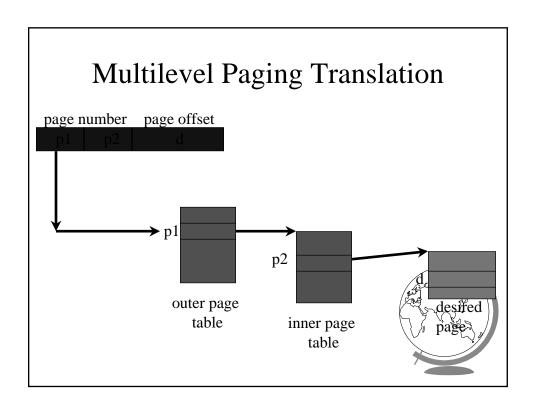

# Large Address Spaces

- Typical logical address spaces:

- -4 Gbytes =>  $2^{32}$  address bits (4-byte address)

- Typical page size:

- -4 Kbytes =  $2^{12}$  bits

- Page table may have:

- $-2^{32}/2^{12} = 2^{20} = 1$  million entries

- Each entry 3 bytes => 3MB per process!

- Do not want that all in RAM

- Solution? Page the page table

- Multilevel paging

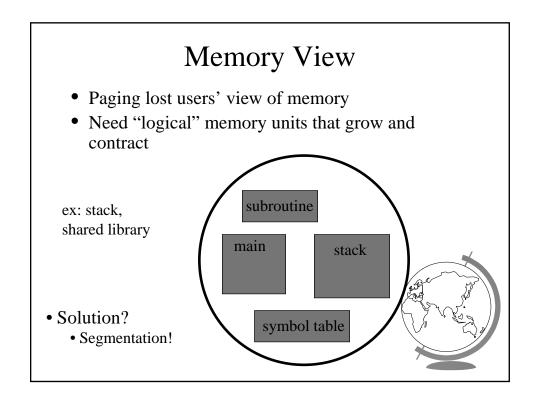

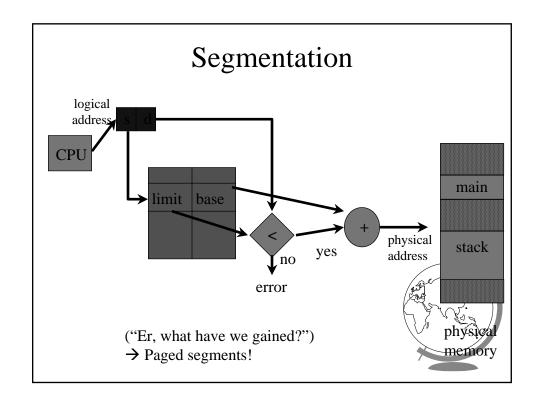

# Segmentation

- Logical address: <segment, offset>

- Segment table maps two-dimensional user defined address into one-dimensional physical address

- base starting physical location

- limit length of segment

- Hardware support

- Segment Table Base Register

- Segment Table Length Register

## Memory Management Outline

• Basic (done)

Fixed Partitions (done)

Variable Partitions (done)

• Paging (done)

- Basic (done)

- Enhanced (done)

• Specific

- WinNT

Linux

# Memory Management in WinNT

- 32 bit addresses ( $2^{32} = 4$  GB address space)

- Upper 2GB shared by all processes (kernel mode)

- Lower 2GB private per process

- Page size is 4 KB (2<sup>12</sup>, so offset is 12 bits)

- Multilevel paging (2 levels)

- 10 bits for outer page table (page directory)

- 10 bits for inner page table

- 12 bits for offset

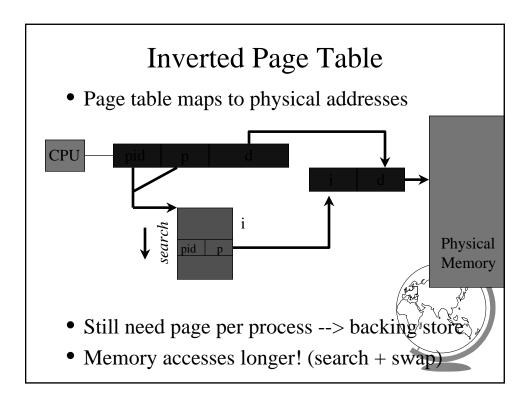

# Memory Management in WinNT

- Each page-table entry has 32 bits

- only 20 needed for address translation

- 12 bits "left-over"

- Characteristics

- Access: read only, read-write

- States: valid, zeroed, free ...

- Inverted page table

- points to page table entries

- list of free frames

# Memory Management in Linux

- Page size:

- Alpha AXP has 8 Kbyte page

- Intel x86 has 4 Kbyte page

- Multilevel paging (3 levels)

- Makes code more portable

- Even though no hardware support on x86

- + "middle-layer" defined to be 1